## enabling heterogeneous hardware acceleration using novel programming and

## scheduling models

enhance

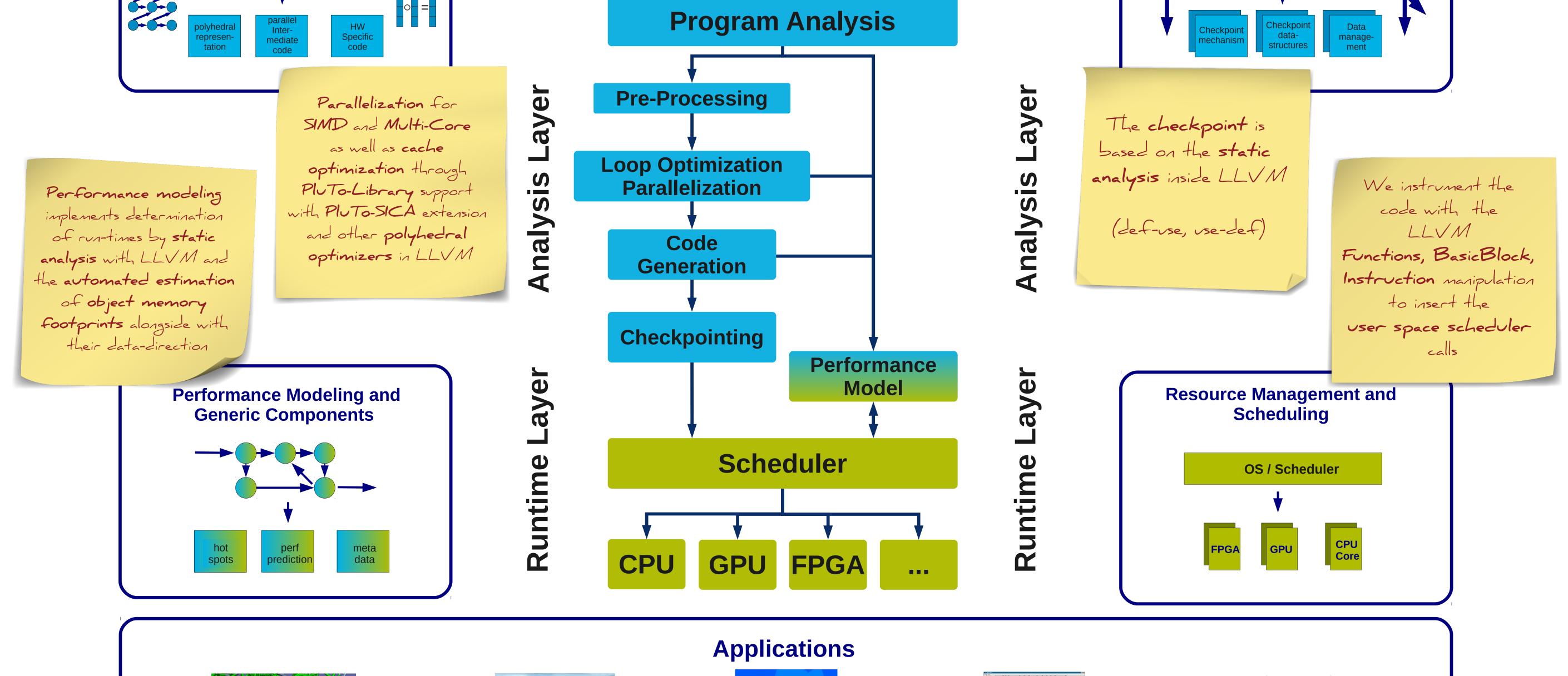

## **PROJECT TOPICS & WORKING PACKAGES**

| Automatic Program Analysis<br>and Semi-Automatic Parallelization | C / C++ / FORTRAN<br>Application | Checkpointing Detection<br>and Insertion |

|------------------------------------------------------------------|----------------------------------|------------------------------------------|

| C / C++ / Fortran                                                |                                  | Intermediate Code                        |

|                                                                  |                                  |                                          |

- Project targets a system platform with Multi-Core, GPU & FPGA processing devices

- **OS** should **schedule** tasks on different processing devices depending on available resources

- Kernel metadata support decision making

- Support the application developer by a tool-chain with semiautomatic parallelization capabilities

- Optimization of loops by transforming memory access patterns

- Hardware aware transformations and optimization approach